بررسی مبحث تایمینگ در حافظه های RAM

RAM Timing

تایمینگ در حافظه های رم به مجموعه ای از بازه های تأخیر گفته می شود که به ترتیب طی می شوند تا عملکرد حافظه ی رم به درستی انجام شود، مهمترین عدد از بین اعداد تایمینگ عدد CL است که با سرعت رم رابطه یه معکوس دارد به طوری که هر چه عدد CL کمتر باشد، سرعت رم بیشتر است و …

بررسی مبحث تایمینگ در حافظه های RAM و تاثیر آن بر سرعت ماژول های رم

مبحث تایمینگ حافظه رم

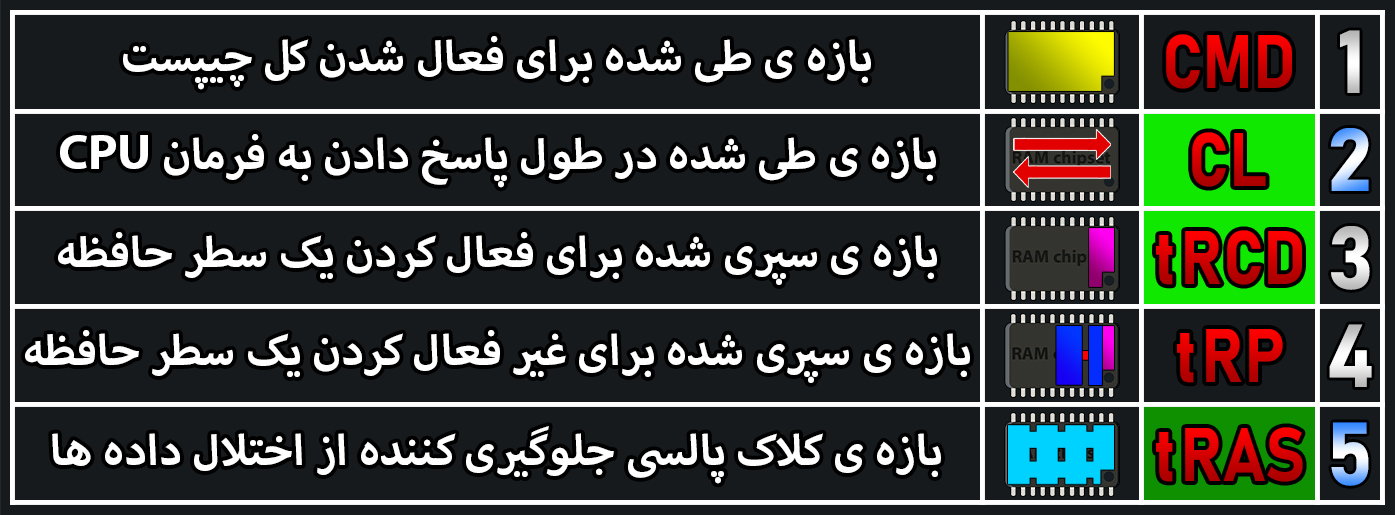

مبحث تایمینگ به طور کلی از چندین بخش زمانی که نشان دهنده ی بازه های تأخیر هستند تشکیل شده است، رم در طی فعالیت خود این بازه های زمانی را سپری می کند تا بتواند دستورات پردازنده را اجرا کند.

برای به دست آوردن سرعت نهایی و مقایسه ی این سرعت در بین ماژول های رم باید تمامی این بازه های زمانی مختلف را به طور کامل مورد بررسی و تحلیل قرار داد، شناخته شده ترین عامل بازه بین بازه های مختلف تایمینگ، بازه یا همان عدد CL است.

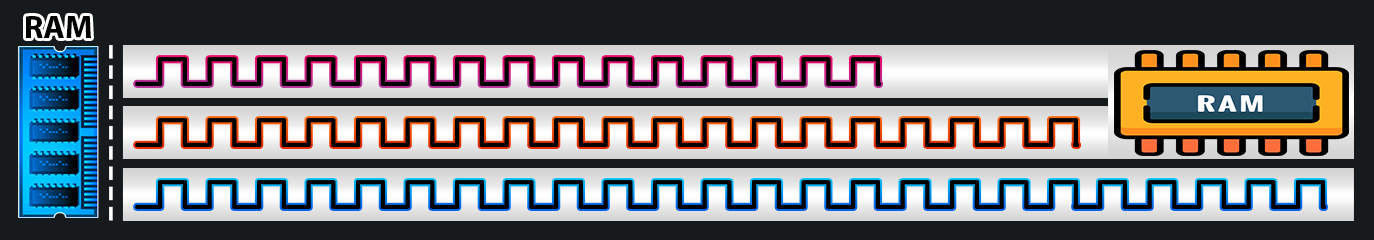

بررسی اصطلاح کلاک پالس

قطعات الکترونیکی مانند رم و پردازنده برای انجام فعالیت های خود، سیکل یا چرخه های عملکرد را با سرعت بسیار بالا انجام می دهند که به هر یک از این سیکل ها کلاک پالس گفته می شود.

برای اجرای هر دستور پردازنده در مازول حافظه ی رم فرآیند یا فرآیند هایی صورت می گیرد، که اغلب اوقات هر یک از آنها از چندین کلاک پالس تشکیل شده است.

الف) فعال سازی چیپست حافظه

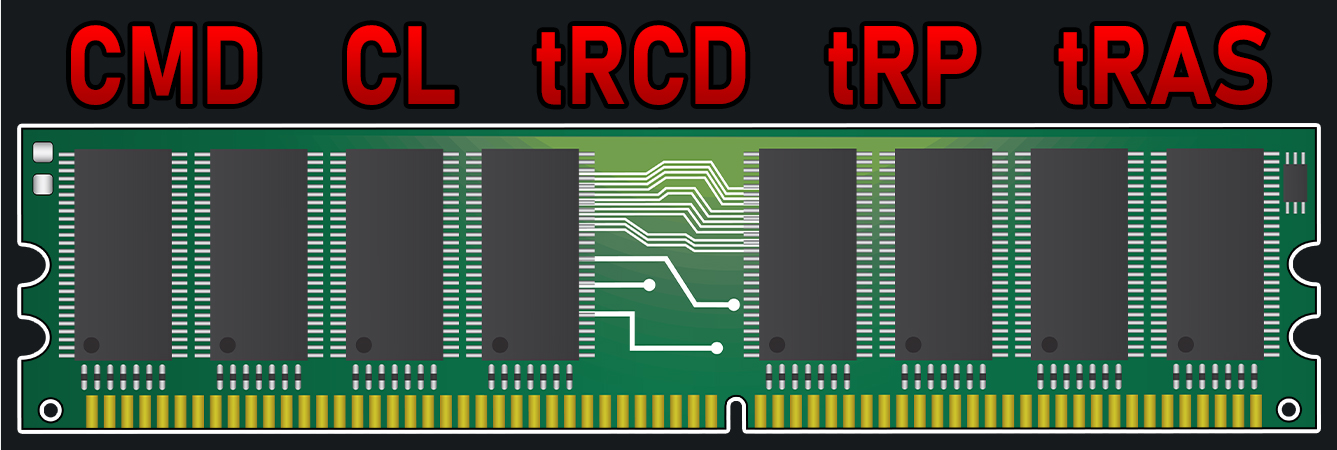

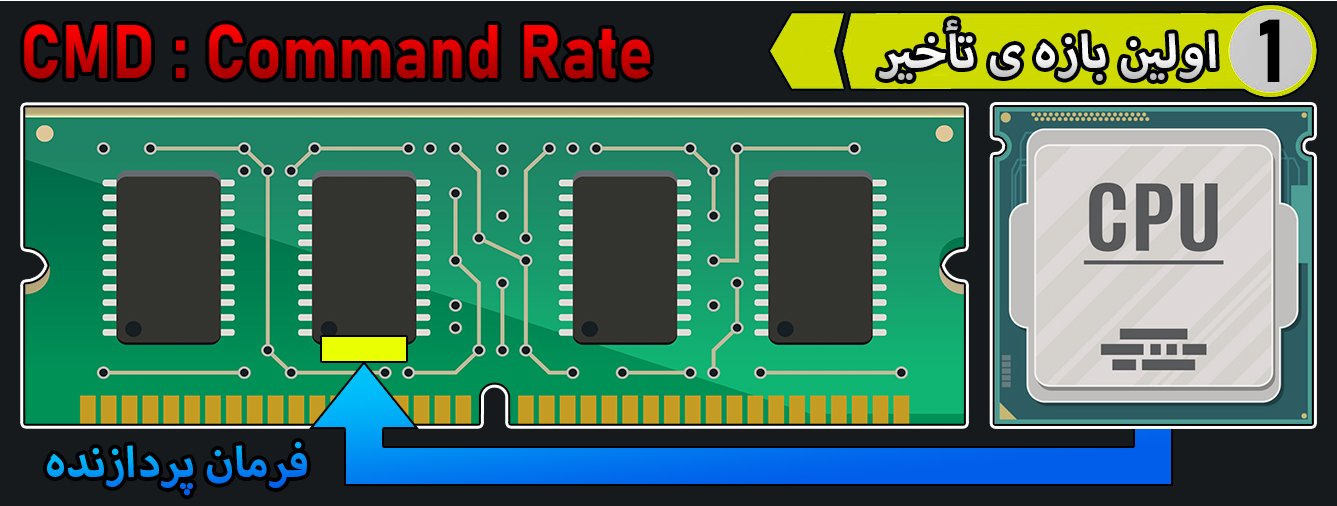

CMD:Command Rate

اولین بازه ی تأخیر در بین اعداد درج شده در تایمینگ ماژول حافظه های رم CMD است، این بازه ی تأخیر از کلاک پالس هایی که در طی فعال سازی چیپست رم بعد از رسیدن فرمان و آغاز عملکرد آن سپری می شوند تشکیل شده است، این بازه بسیار کوتاه مدت و در حد چند کلاک پالس است.

(اطلاعات این بازه کلاک پالسی به دلیل کوتاه بودن آن اغلب مورد بررسی قرار نمی گیرد)

ب) پاسخ دهی به فرمان پردازنده

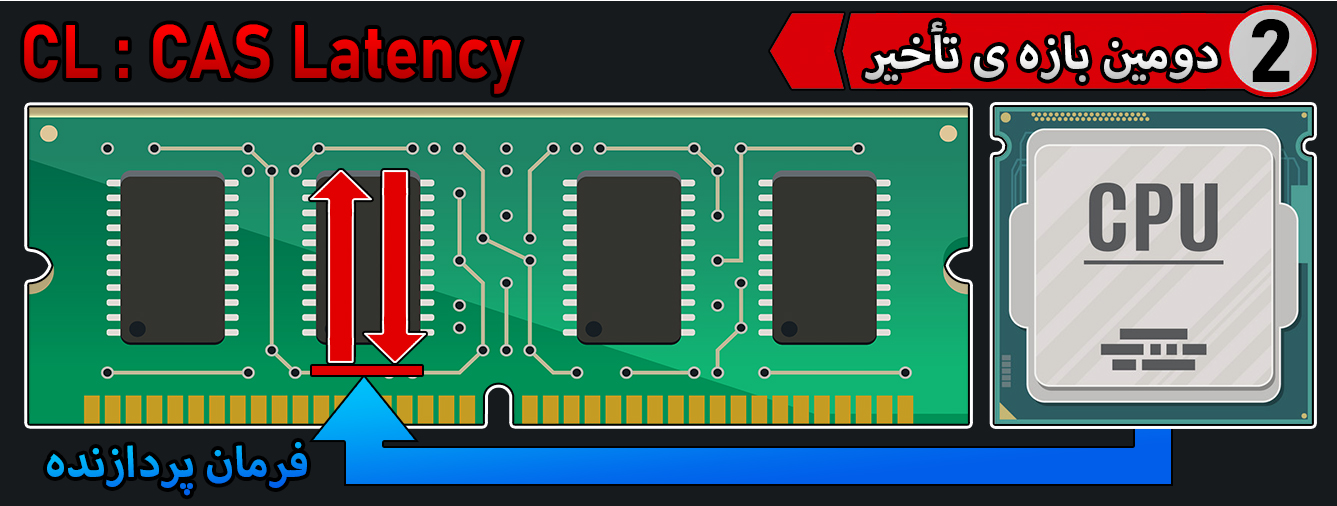

CL:CAS Latency

عدد CL به معنی تعداد کلاک پالسی است که طی می شود تا حافظه ی رم به دستور رسیده از پردازنده پاسخ دهد، یعنی کلاک پالس هایی که از ورود فرمان پردازنده به ماژول رم تا خارج کردن داده های از چیپست حافظه سپری می شوند.

(در بین بازه های تأخیر تایمینگ همپوشانی های زمانی های متعددی مشاهده می شود)

ج) فعال سازی سطر در ماتریس

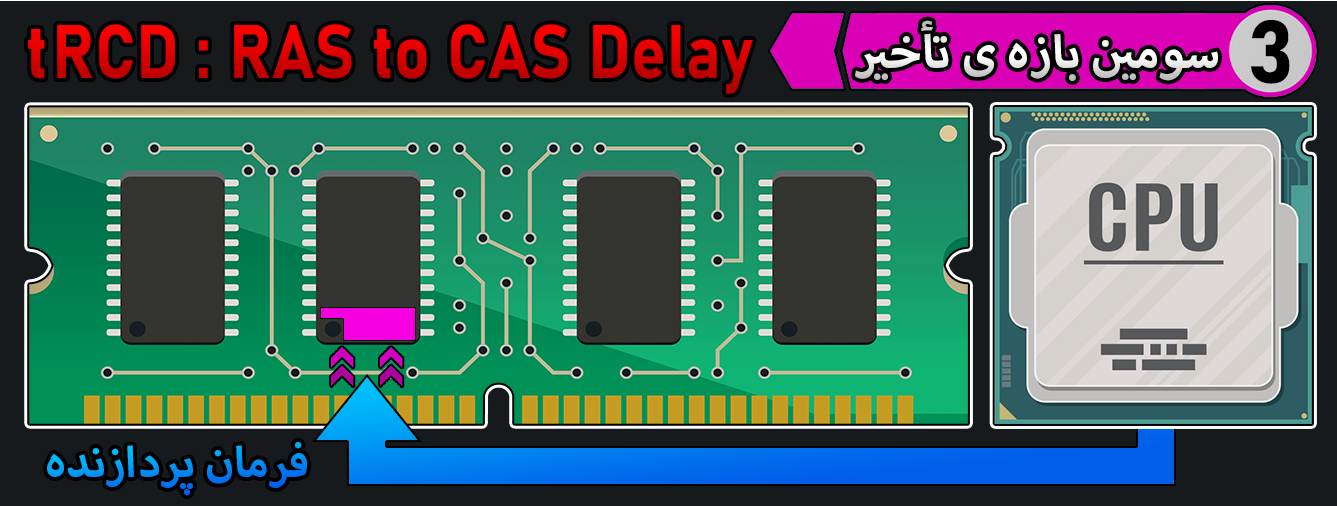

tRCD:RAS to CAS Delay

این بازه ی تأخیر به معنی کلاک پالس هایی است که چیپست حافظه رم برای فعال سازی بخضی از خود که اصطلاحاً سطر نامیده شده و داده های مورد نظر را در خود ذخیره سازی کرده است، به انجام می رساند.

(در ادامه موضوعات سطر و ماتریس به طور کامل مورد بررسی قرار می گیرند)

ه) سیکل های جلوگیری از اختلال

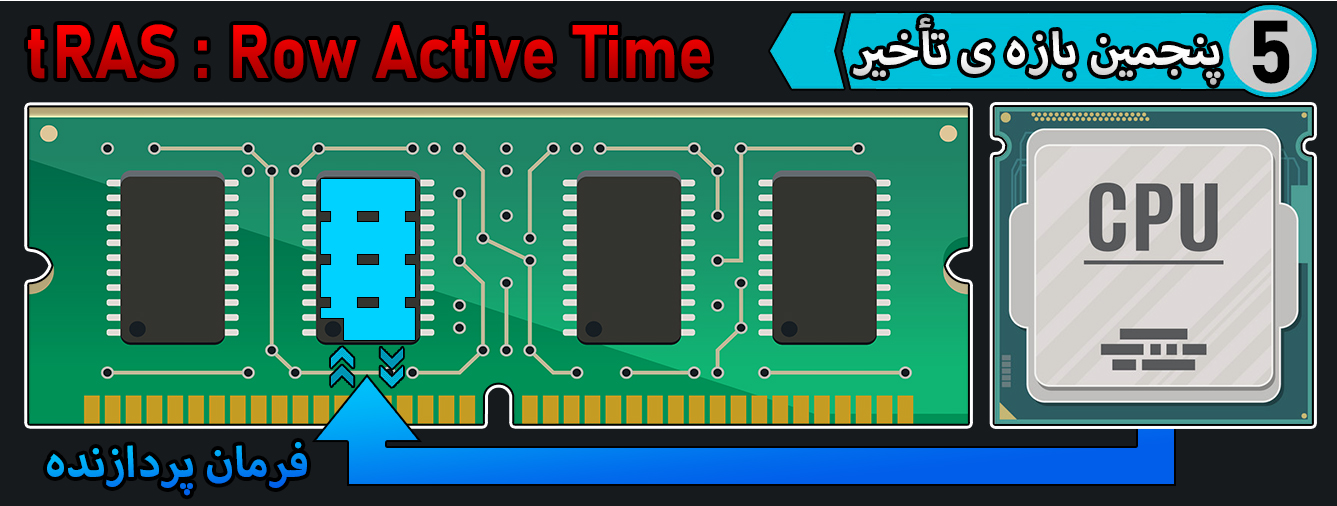

tRAS:Row Active Time

پنجمین بازه ی تأخیر کلاک پالسی بعنی tRAS به منظور جلوگیری از اختلال طی می شود، این بازه ی کلاک پالسی از آغاز رسیدن دستور از سمت پردازنده به چیپست حافظه ی رم تا نزدیک به خروج داده ها از حافظه ی رم سپری می شود، این بازه ی تأخیر باعث خروج کامل، صحیح و بدون اختلال داده ها از ماژول رم می شود.

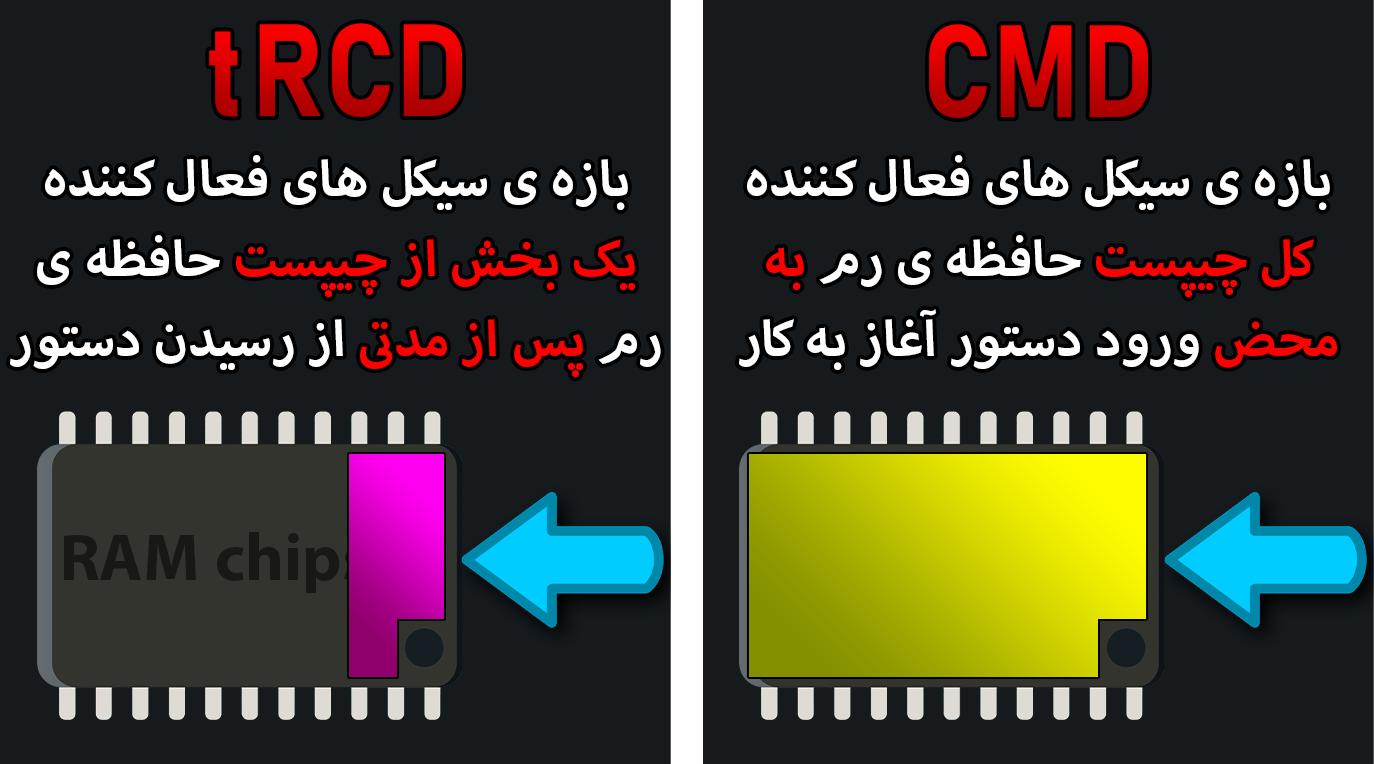

بررسی تفاوت بازه های تأخیر CMD و TRCD

:CMD

این بازه ی تأخیر به معنی سیکل های فعال کننده ی کل چیپست حافظه ی رم به محض ورود دستور آغاز به کار است.

:tRCD

این بازه ی تأخیر نشان دهنده ی سیکل های فعال کننده ی یک بخش از چیپست حافظه ی رم پس از مدتی از رسیدن دستور آغاز به کار می باشد.

تفسیر موضوعات سطر و ماتریس در ماژول حافظه RAM

ماتریس: مجموعه ای که به صورت بسیار منظم، در دسته ها و بخش های گسترده ی زیادی طبقه بندی شده و اطلاعات پردازشی را در بخش های مختلف خود ذخیره سازی می کند.

سطر: اگر هر چیپست حافظه ی رم به صورت یک ماتریس در نظر گرفته شود، هر یک از بخش های آن که داده ها را ذخیره سازی می کند یک سطر نامیده می شود.

بررسی ترتیب وقوع بازه های تأخیر

اولین رخداد در عملکرد حافظه ی رم، رسیدن دستور از پردازنده توسط مادربرد به ماژول رم ها و سپس در صورت وجود قسمت بافر، ورود به آن و یا بخش های اکترونیکی مشابه آن در ماژول رم است.

سپس به ترتیب بازه های تأخیر زیر طی می شوند: (از چپ به راست)

CMD – CL – tRCD – tRP – tRAS

مقالات مرتبط

پیکربندی حافظه رم (تک کاناله – چند کاناله) / RAM configuration

پیکربندی حافظه های رم (تک کاناله – چند کاناله) RAM

بررسی مبحث فرکانس در حافظه RAM

بررسی مبحث فرکانس در حافظه های RAM RAM frequency فرکانس

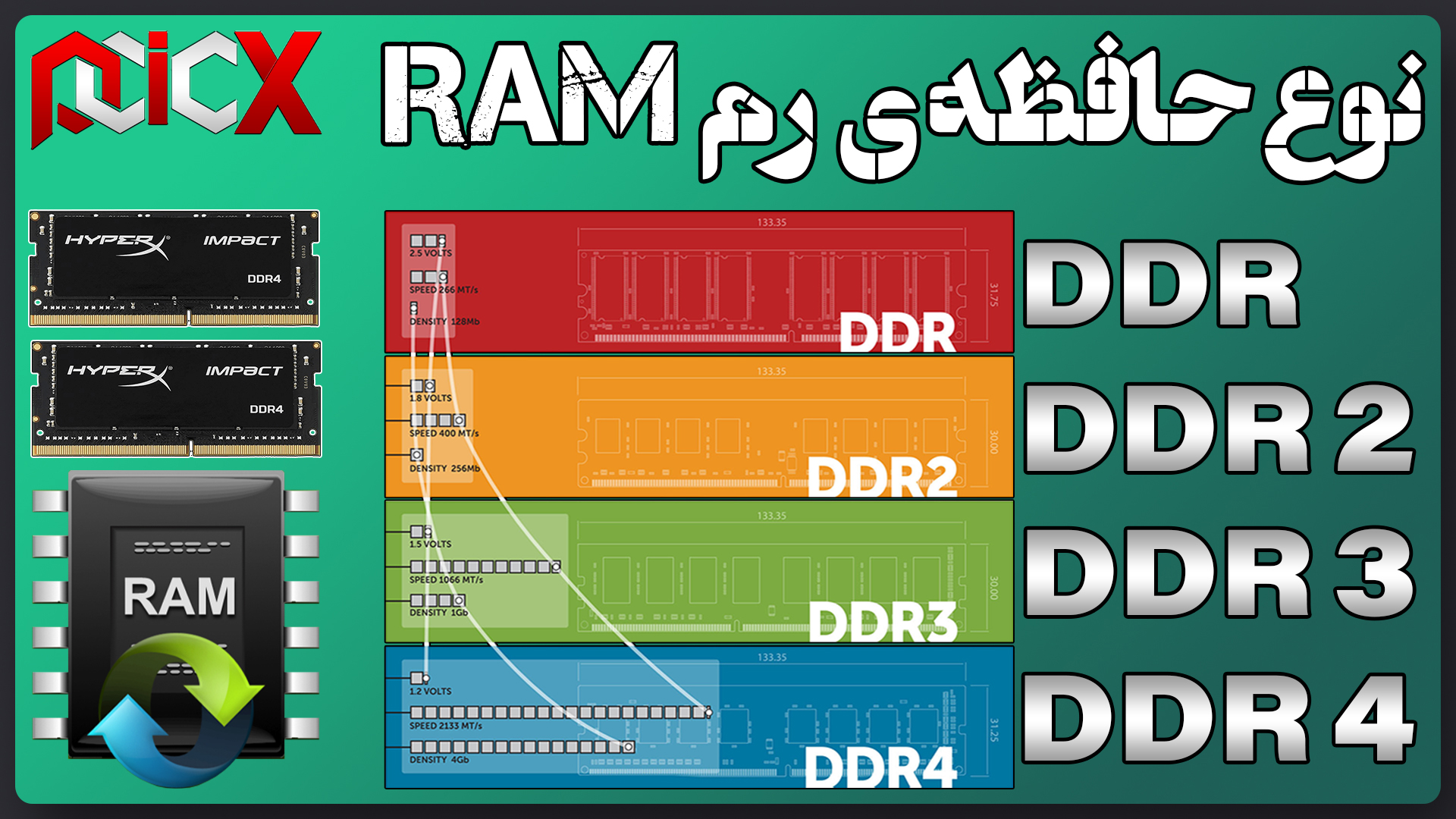

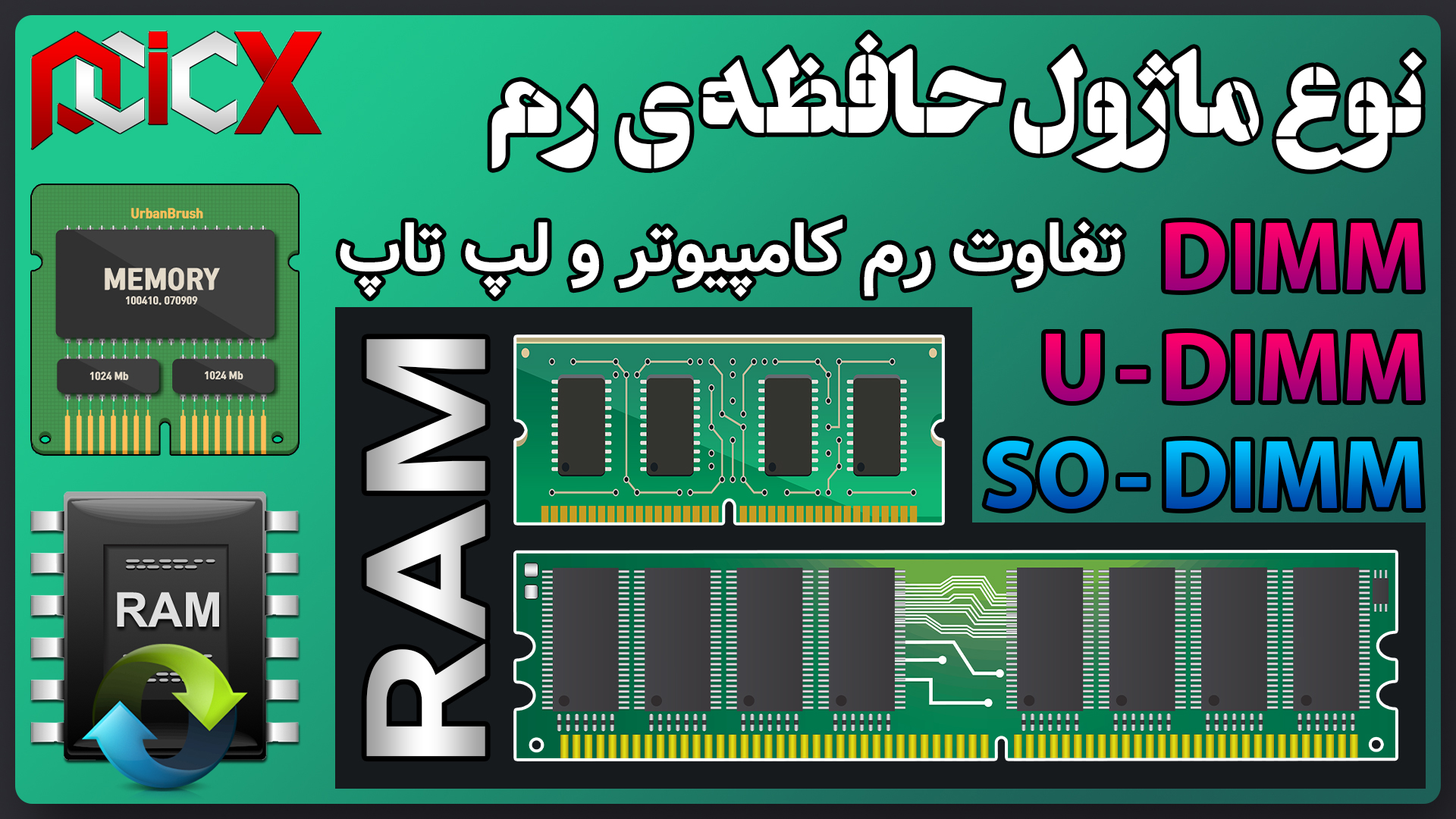

انواع ماژول حافظه رم / RAM module type

انواع ماژول های حافظه های RAM RAM module type انواع

ظرفیت مناسب در حافظه رم / RAM capacity

ظرفیت مناسب هر کاربری در حافظه RAM RAM capacity ظرفیت

RAM